❯

Remote Software Development Without Compromising Quality

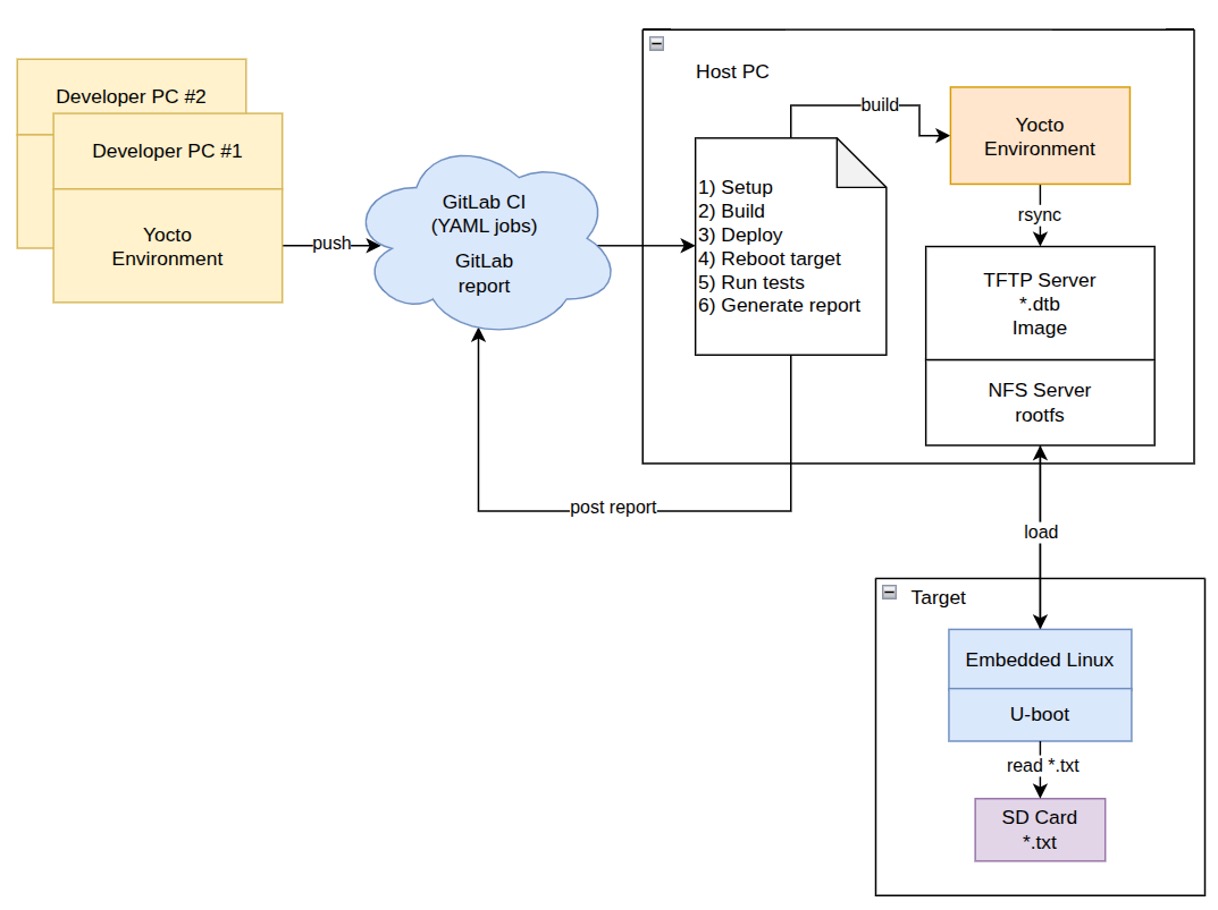

At EmTech S.A., we develop embedded software systems in highly demanding environments, where delivery quality depends not only on code but also on strict control over toolchains, build systems, and access to real hardware. In this context, remote collaboration introduces additional complexity: distributed teams must maintain consistency across development setups, integration workflows, and validation infrastructure. To address this challenge, EmTech has built an operational model that enables fully remote embedded development without sacrificing efficiency, reproducibility, or engineering rigor.

%20(1).jpg)

.webp)

.webp)

.webp)

.webp)

_de%20(1).jpg)

.png)

.png)

%20(3).png)

.png)